Кремнієвий чип із шарами фосфіду індію здатний працювати на терагерцових частотах |

| Saturday, 22 December 2012 |

|

Нові високопродуктивні чипи створені на основі нової гібридної напівпровідникової технології можуть стати основою систем, що вимагають величезної обчислювальної потужності, таких як суперкомп'ютерні системи, системи обробки візуальної інформації, медичних систем, технологій безпеки і нових надширокосмугових систем мобільного зв'язку. "Наш ентузіазм підстьобувало те, що, незважаючи на всі попередні спроби, нікому ще не вдавалося створити надійного" інтерфейсу "між двома абсолютно різними технологіями напівпровідників" - розповів Вольфганг Хайнріх (Wolfgang Heinrich), вчений з інституту FBH, який проводив ці дослідження спільно з Берндом Тіллеком (Bernd Tillack), вченим з інституту IHP. - "Нам вдалося успішно поєднати обидва технологічних процеси у єдине ціле, притому ми зробили це настільки бездоганно, що створені напівпровідникові схеми працюють на таких тактових частотах, про які раніше тільки можна було лише мріяти". Звичайні чипи, виготовлені за кремнієвою технологією CMOS (Complementary Metal Oxide Semiconductor), володіють одним істотним недоліком. Коли тактові частоти їх роботи починають наближатися до позначки 100 ГГц, поріг напруги пробою напівпровідників різко знижується, що накладає обмеження на робочу напругу чипів і вихідну потужність сигналів. Для подолання цього обмеження команди інститутів IHP і FBH об'єднали стандартні кремнієві напівпровідникові ланцюги, виготовлені за технологією CMOS із шарами фосфіду індію, внаслідок чого вийшли складні багатошарові структури. Але фосфід індію зіграв роль своєрідного ізолятора, сильно підняв поріг напруги пробою, і це дозволило отримати високу потужність вихідних сигналів на високій тактовій частоті роботи чипа.

Для того, щоб змусити працювати гібридну напівпровідникову технологію дослідникам довелося вдатися до кількох технологічним прийомів. По-перше, їм довелося злити воєдино два середовища програмного забезпечення комп'ютерного проектування, які враховують особливості кожної з складових частин гібридної технології. По-друге, дослідникам довелося забезпечити дуже високу точність виготовлення елементів напівпровідникових чипів, які повинні були бути відтворені з точністю не менше 10 нм. Оскільки у гібридної технології за основу була взята стандартна CMOS-технологія, то чипи будуть виготовлятися на існуючому обладнанні, а витрати на їх виробництво будуть знаходитися на рівні витрат на виробництво звичайних кремнієвих чіпів, що визначають вартість сучасної електроніки. Наступними кроками, які мають намір здійснити німецькі дослідники, буде пошук рішень, що дозволяє стабілізувати виробничий процес для отримання ще більшої точності виготовлення, і оптимізувати будову напівпровідникових компонентів, елементів і ланцюгів, роблячи їх придатними для нових технологічних виробничих процесів.

Джерело: InfoNova.org.ua За матеріалами: dailytechinfo.org

Наступні новини у розділі:

Попередні новини у розділі:

|

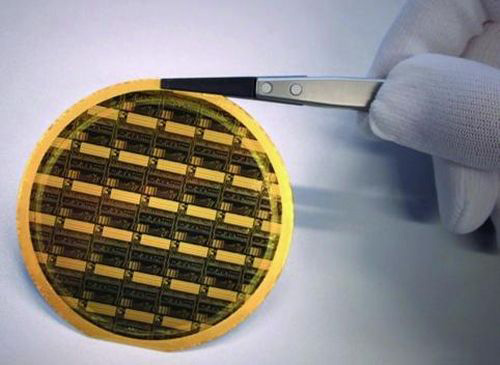

Дослідники з Інституту Фердинанда Брауна (Ferdinand Braun Institut, FBH) у Берліні і дослідного інституту Innovations for High Performance Microelectronics (IHP) у Франкфурті зуміли об'єднати дві технології виготовлення різних видів напівпровідників на одному кристалі чипа. Комбінація кремнієвих напівпровідникових елементів і елементів з фосфіду індію дозволяє забезпечити роботу логічних мікросхем, у тому числі і мікропроцесорів, на терагерцових тактових частотах. При цьому, для виробництва таких кристалів чипів не потрібна корінна перебудова існуючих технологічних виробництв.

Дослідники з Інституту Фердинанда Брауна (Ferdinand Braun Institut, FBH) у Берліні і дослідного інституту Innovations for High Performance Microelectronics (IHP) у Франкфурті зуміли об'єднати дві технології виготовлення різних видів напівпровідників на одному кристалі чипа. Комбінація кремнієвих напівпровідникових елементів і елементів з фосфіду індію дозволяє забезпечити роботу логічних мікросхем, у тому числі і мікропроцесорів, на терагерцових тактових частотах. При цьому, для виробництва таких кристалів чипів не потрібна корінна перебудова існуючих технологічних виробництв.